74HC595是硅结构的高速CMOS器件,兼容低电压TTL电路,遵守JEDECNO。7A标准。74HC595拥有8阶串行移位寄存器,带有存储寄存器和三态输出。移位寄存器和存储寄存器分别都是采用单独的时钟。

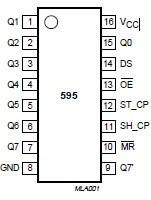

一、74HC595引脚说明

1、Q1~Q7(1~7引脚):其中1脚和OE一样用作使能端及并行数据输出,而2~6脚是数据输入,7脚是并行数据输出。

2、GND(8引脚):接地电源,

3、QT(9引脚):串行数据输出,

4、MR(10引脚):主复位(低电平0),MR为低电平时,紧紧影响移位寄存器而以。

5、SH_CP(11引脚):移位寄存器时钟输入,每一个时钟信号将移入一位数据到寄存器。

6、ST_CP(12引脚):存储寄存器时钟输入,当输入的数据在传入寄存器后,只有供给一个锁存信号才能将移入的数据送QA~QH口输出。移位寄存器内容移入,先前的移位寄存器的内容到达保持寄存器并输出。

7、OE(13引脚):输出有效(低电平0),即三态输出使能端低电平有效。当该引脚上为“1”时QA~QH口全部为“1”,为“0”时QA~QH的输出由输入的数据控制。

8、DS(14引脚):串行数据输入口,显示数据由此进入,必须有时钟信号的配合才能移入。

9、Q0(15引脚):并行数据输出,移位寄存器的内容到达保持寄存器并从并口输出。

10、VCC(16引脚):接电源正极。