众所周知,将铅加入到锡中可减少锡晶须的危害,因为铅改变了机械特性,即铅提供了更高的固有潜变速率,降低了屈服应力并且减轻了杂质对机械特性的影响。此外,铅在界面分离,增加了晶粒边界的流动性,提高了晶粒边界和表面源作为潜变空位的效率,改善了表面氧化物的连续性,并改变了IMC的形态。铅通过在电沉积期间增加晶粒成核速率来改变电沉积行为,并提供电解质以产生具有较小有机和无机杂质水平的沉积物。

所以,电子元器件上的引出端镀层通常是采用锡铅合金,来抑制锡晶须的生长。但随着欧盟颁布RoHs《电气、电子设备中限制使用某些有害物质指令》以后,主要对电子产品中的Pb、Cd、Hg、Cr6+PBBs及PBDEs六种有害物质进行了限制。所以,smt贴片打样企业为了适应市场变化,制造工艺也逐渐走向无铅化,引出端镀层采用纯锡及锡合金(锡铋和锡银)取代了锡铅合金。但纯锡和锡合金电沉积及浸焊后会生长出锡晶须,从而会发生引出端之间短路、电弧放电或降低电气及机械性能等现象,随着电子元器件高密度及小型化发展,引出端的间距也在不断减小,这就增加了锡晶须带来的可靠性隐患。

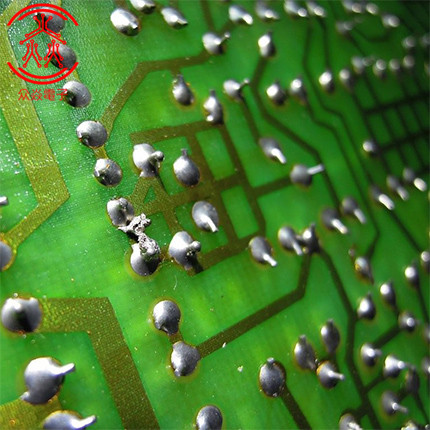

晶须是一种柱状或圆柱形的细丝,通常为单晶体结构,从固体表面生长出来,锡须也符合晶须的特征。JESD22A121《锡和锡合金表面晶须生长的试验方法》对于晶须的定义为:长宽比(长/宽)大于2,呈现扭结状、弯曲状、小丘状或柱状等不同形态,具有均匀的横截面形状(或由很少的分叉单根柱状细丝组成),具有环状及条纹状生长或是交错生长方式,长度为10μm或更长。

关于锡晶须的生长,比较有代表性的生长机制有压应力理论、再结晶理论及位错理论等。但目前尚未有人们普遍接受的一种生长机理,晶须生长机理仍然是最热门的研究之一。下面众焱电子小编就来为大家介绍一下这三种理论。

1、压应力理论

电镀之后的锡镀层内部存在一定残余应力,通过对锡晶须的表面形貌(存在纵向凹坑)观察可知,推测晶须的生长是镀层残余应力挤压的结果。铜元素扩散到锡晶粒边缘形成了金属间化合物,促使镀锡层内部应力增加,导致锡原子晶界边缘扩散形成锡晶须。

2、再结晶理论

镀层中存在晶体缺陷的条件下,锡晶粒会发生再结晶,而晶须就是这种特殊晶粒在空间上自由生长的表现。但根据资料显示,目前尚未有人观察到镀锡层晶颗粒在室温下放置后,发生了晶粒再结晶现象以及晶须生长前后镀锡层的晶粒尺寸和形状纯在明显差异。另外,温度的升高一般会促进晶须的生长,但大量的研究数据显示锡晶须在室温下生长速度较快,超过127℃后晶须生长会被抑制。

3、位错理论

假设锡晶须中心有一根螺位错,由于螺位错的终端存在着表面露头的生长台阶,锡原子可以沿着位于晶须中心的螺位错以不断填补台阶的方式生长。

影响锡晶须生长的因素很多,包括应力大小、金属间化合物、镀层晶粒大小及择优取向、基体材料、镀层厚度、温度及环境、电镀工艺等等。

广州众焱电子有限责任公司www.gz-smt.com,是一家专业从事SMT贴片加工、DIP常见加工、PCBA包工包料、PCB线路板制造的公司,拥有多年的电子加工经验,以及先进的生产设备和完善的售后服务体系。公司的SMT贴片加工能力达到日产100万件,DIP插件加工产能为20万件/日,能够给你提供优质的电子加工服务。